HEP Instrumentation

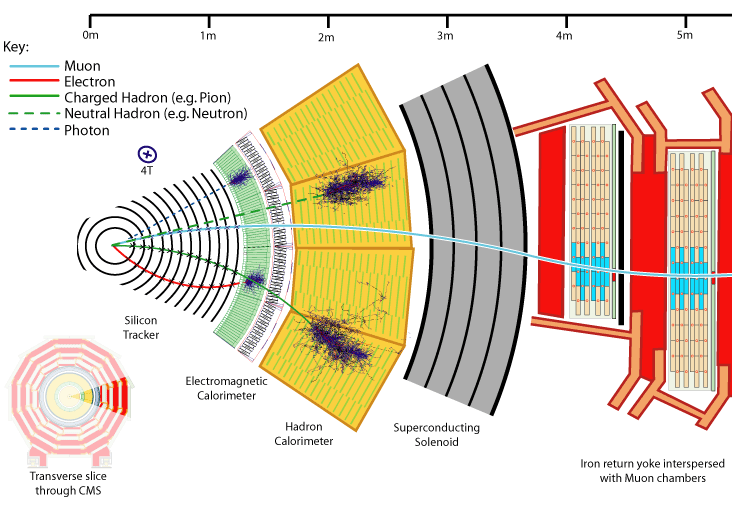

The Large Hadron Collider (LHC) is the biggest particle accelerator ever made. Its main component is a 27 km long ring-shaped underground tunnel located near Geneva, crossing the border between France and Switzerland. The Compact Muon Solenoid (CMS) is one of the two general purpose experiments of the LHC, designed to investigate any conceivable physical phenomena related to the particle collisions. The CMS detector is made of several layers of specialized sub-detectors that measure the different characteristics of the particles produced in the 40 million collisions that happen every second in the LHC.

As the number of events is immense, selecting the most interesting ones becomes essential. Every second, 40 Terabytes of data is produced; and in a single day, 3.5 million Terabytes. That is more than 5000 times the amount of data Facebook produces in the same period! In order to cope with the huge amount of information, LHC has a very fast processing chain which analyses the upcoming data and decides if the current event is worth saving or not. Only 1 in about 40,000 events is stored.

LHC Phase-2 Upgrade

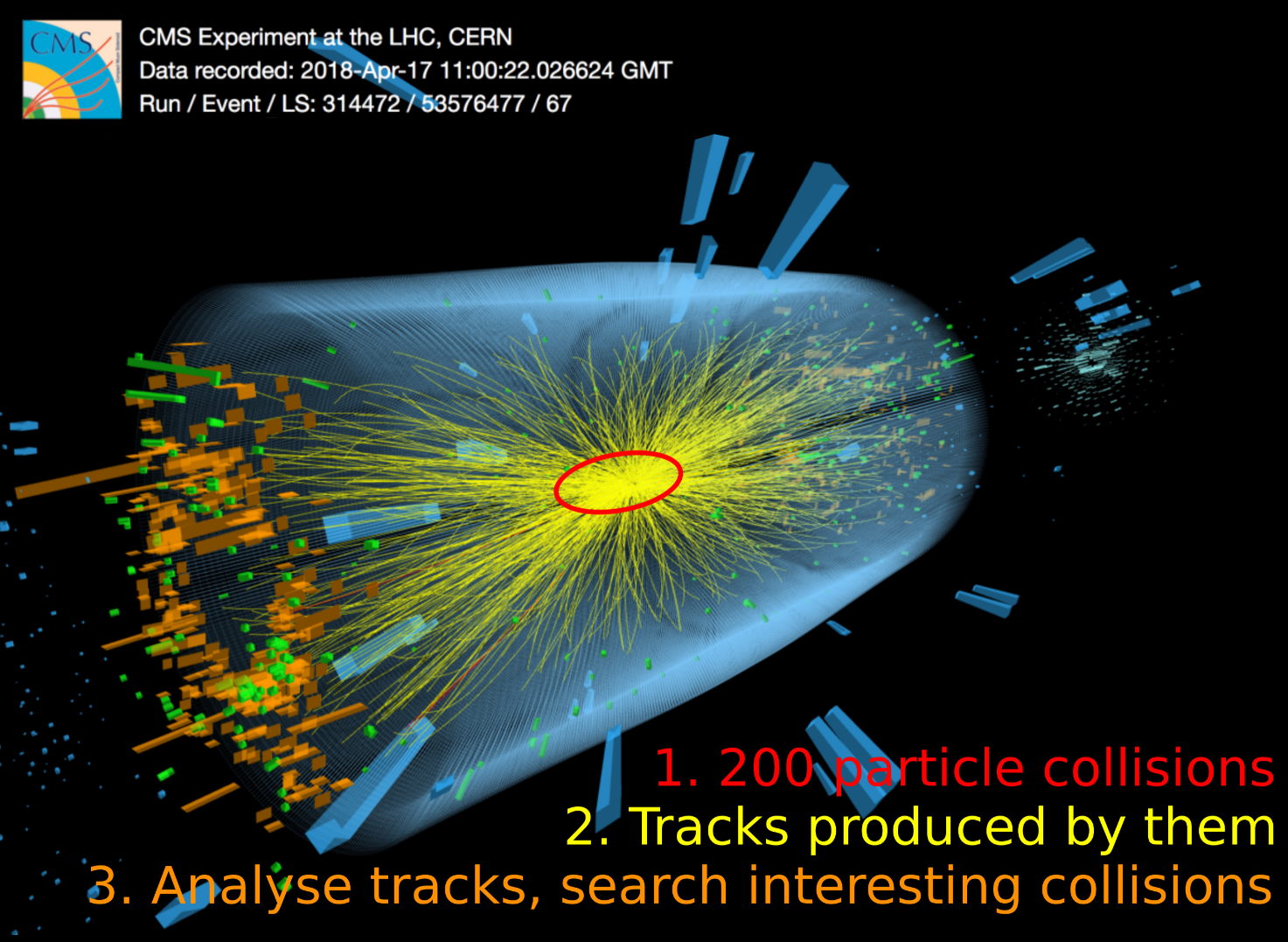

In 2026 LHC will be upgraded and the number of particle collisions in every event will go from 20 to 200. As a result, the available sample of events will grow and we will be able to investigate rare phenomena with greater precision.

As the accelerator is upgraded, its experiments must also undergo major overhaul to cope with the higher luminosity and to optimize the detectors’ performance. The operation in this high-luminosity program is referred to as High-Luminosity LHC (HL-LHC) or “Phase 2”. Given the fast processing required, the algorithm will not run on software, but rather on programmable boards with specific integrated circuits called FPGA’s, in which we can implement the algorithm directly in hardware, optimizing performance and latency.

Our research

Among the several proposed upgrades for the Compact Muon Solenoid (CMS) detector there is the complete replacement of the Outer Tracker and the Pixel detector, which are currently unable to operate under the conditions required by the HL-LHC. The new Outer Tracker will be in compliance with the Level 1 (L1) tracker upgrade (increase of L1 rate to 750 kHz, to be processed under a maximum latency of 12.5 us) and will add tracking information to the L1 trigger decision.

The SPRACE Instrumentation team participates in several fronts of the electronic instrumentation development for the CMS Phase 2 upgrade. Between 2014 and 2017 we were in collaboration with the Fermi National Accelerator Laboratory (Fermilab) to develop a Level-1 Track Finder for the CMS detector Tracker based on Associative Memories and FPGA’s (AM+FPGA). During this period we worked in different areas involving the Pulsar2b (see http://www-ppd.fnal.gov/ATCA/) card for AdvancedTCA shelves:

IPMC

IPMC (Intelligent Platform Management Controller): An ARM Cortex M3 micro-controller responsible for the monitoring and control of ATCA blades in accordance to PICMG standard. The micro-controller firmware was tailored for Pulsar 2b cards, so it optimally provides cooling control, power management and system configuration for these boards.

XVC Service

Xilinx Virtual Cable (XVC) Service: A service implemented on the IPMC used for remote programming and debugging of Xilinx FPGAs. The XVC service mediates the communication between a remote PC and the FPGA’s, receiving data over TCP/IP from a Xilinx Hardware Server running on the remote PC side and translating it to JTAG in order to communicate with the FPGA’s.

Data Sourcing

Data Sourcing System: A general-purpose implementation of a data sender and receiver aimed to operate in the same data transmission conditions as the CMS detector. This project used the high-speed interfaces present on Pulsar 2b to emulate the data flow from the detector, allowing algorithm debugging and benchmarking of the AM+FPGA Track Finder.

In 2018 SPRACE became a Tracker Institution, officiating the group’s commitment on contributing to the Phase-2 Tracker Upgrade efforts. Our objective is to develop the Front-End of the Data Trigger and Control (FE-DTC), the processing stage responsible for interfacing with the detector, collecting data from its hybrid modules, organizing it and delivering it downstream on the processing chain. As a Tracker Institution, we are not only contributing with our technical expertise on the development, but also financially supporting the DTC hardware production.